Datasheet

## **PWM-Embedded 3x4-Channel Constant-Current** Sink Driver for LED Strips

### Features

- 3x4-channel constant-current sink driver for LED strips

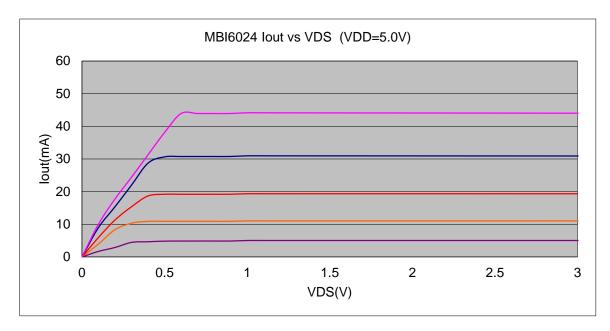

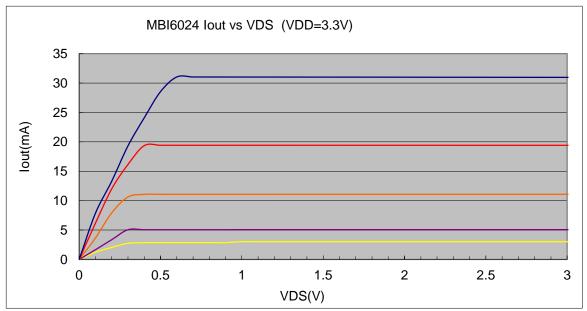

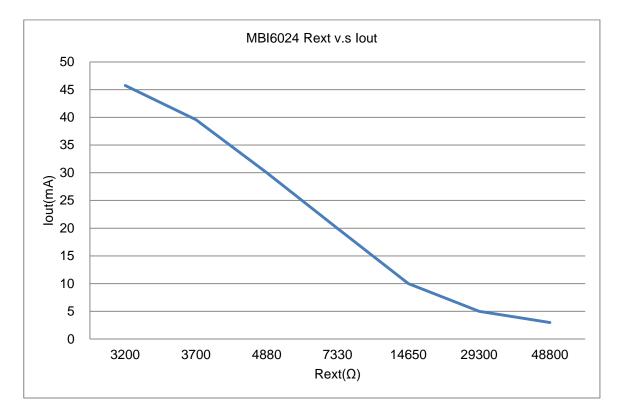

- Constant current range: 3~45mA

- 3 groups of output current, each group is set by an external resistor

- Sustaining voltage at output channels: 17V (max.)

- Supply voltage 3V~5.5V

- Embedded 16-bit PWM generator

- Gray scale clock generated by the embedded oscillator

- S-PWM patented technology

- Two selectable modes to trade off between image guality and transmission bandwidth

- 16-bit gray scale mode (with optional 8-bit dot correction)

- 10-bit gray scale mode (with optional 6-bit dot correction)

- Reliable data transmission

- Daisy-chain topology

- Two-wire transmission interface

- Phase-inversed output clock

- Built-in buffer for long distance transmission

- Flexible PWM reset modes

- Auto-synchronization mode

- Manual-synchronization mode

- Selectable polarity reversion to drive high-power drivers or MOSFET

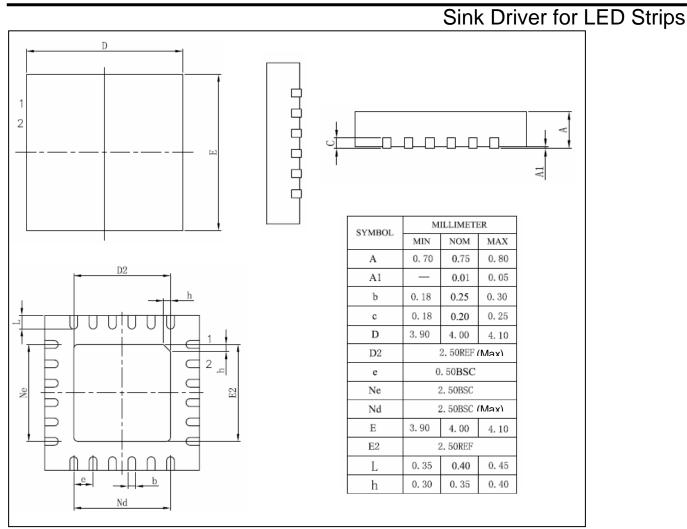

- **RoHS-compliant packages**

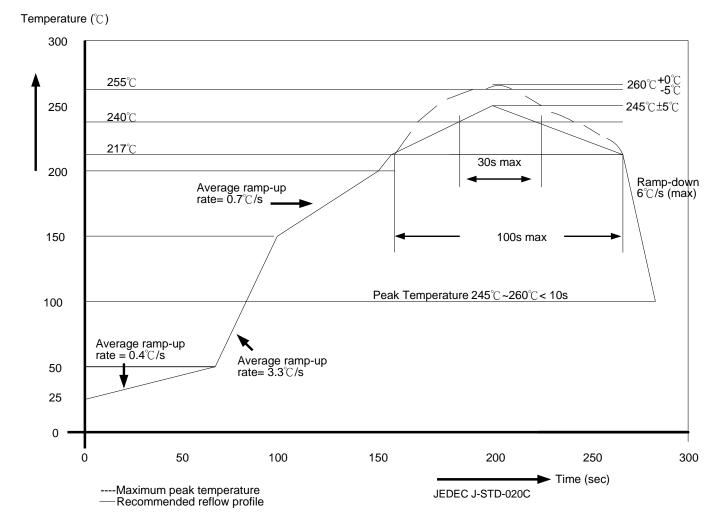

- Package MSL Level: 3

## **Application**

- LED strips

- Mesh display

- Architectural lighting

## **Product Description**

MBI6024 is a 3x4-channel, constant-current, PWM-embedded sink driver for LED strips. MBI6024 provides constant current ranging from 3mA to 45mA for each output channel and are adjustable with three corresponding external resistors. Besides, MBI6024 can support both 3.3V and 5V power systems and sustain 17V at output channels.

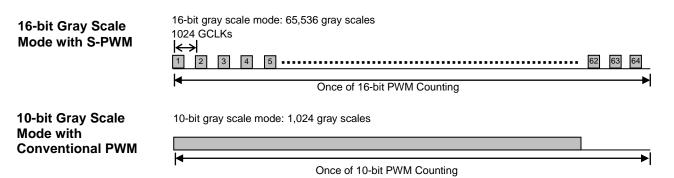

With Scrambled-PWM (S-PWM) technology, MBI6024 enhances pulse width modulation by scrambling the "on" time into several "on" periods to increase visual refresh rate at the same gray scale performance. Besides, the gray scale clock (GCLK) is generated by the embedded oscillator. Moreover, MBI6024 provides two selectable gray scale modes to trade off between image quality and transmission: 16-bit gray scale mode and 10-bit gray scale mode. The 16-bit gray scale mode provides 65,536 gray scales for each LED to enrich the color. Subject to the 16-bit gray scale mode, the 8-bit dot correction may adjust each LED by 256-step gain to compensate the LED brightness. Furthermore, the 10-bit gray scale mode provides 1,024 gray scales. Subject to the 10-bit gray scale mode, 6-bit dot correction may adjust each LED by 64-step gain.

In addition, MBI6024 features a two-wire transmission interface to make cluster-to-cluster connection easier. To improve the transmission quality, MBI6024 provides phase-inversed output clock to eliminate the accumulation of signal pulse width distortion. MBI6024 is also flexible for either manual-synchronization or auto-synchronization. The manual-synchronization is to maintain the synchronization of image frames between ICs. The auto-synchronization is to achieve accurate gray scale, especially when using the built-in oscillator. In addition, MBI6024 preserves selectable polarity reversion to drive high-power drivers or MOSFET as a PWM controller.

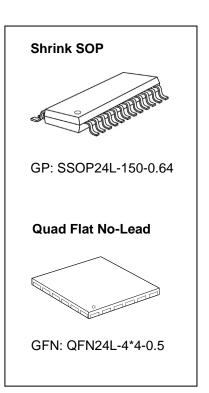

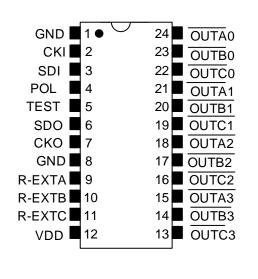

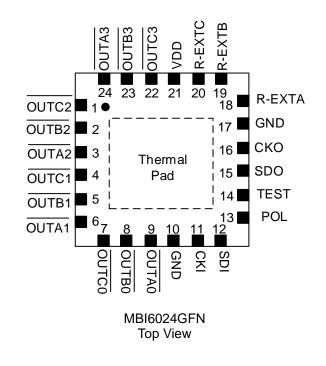

## **Pin Configuration**

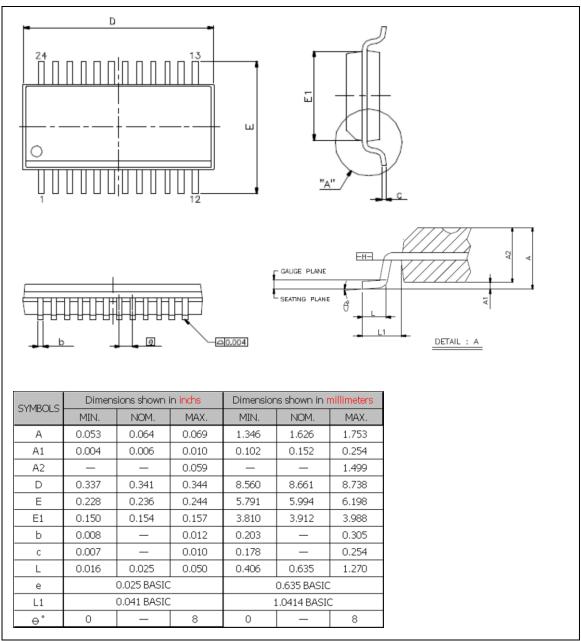

MBI6024GP Top View

#### Pin Name **Description and function** GP GFN 1 10 GND Ground terminal 2 11 CKI Input terminal for clock input 3 12 SDI Input terminal for serial data input Input terminal for selecting output polarity Internal pull-high POL High: drive LED or low-active regulators or PMOS 4 13 Low: output reversed to work as a PWM controller to drive high-active regulators or NMOS TEST Test pin (Default: internal pulled- low) 5 14 6 15 SDO Output terminal for serial data output 7 16 CKO Output terminal for clock output 8 17 GND Ground terminal Input terminals for setting output current by connecting to an 9,10,11 18,19,20 R-EXTA, B, C external resistor VDD 12 21 3.3V/5V supply voltage terminal 15,14,13 24,23,22 OUTA3, B3, C3 Output terminals for constant-current output 18,17,16 OUTA2, B2, C2 3,2,1 Output terminals for constant-current output 21,20,19 6,5,4 OUTA1, B1, C1 Output terminals for constant-current output 24,23,22 9,8,7 OUTA0, B0, C0 Output terminals for constant-current output Heat dissipation pad\* Thermal Pad --Please connect to GND.

\*The desired thermal conductivity will be improved on condition that a heat-conducting copper foil on PCB is soldered with thermal pad.

## **Terminal Description**

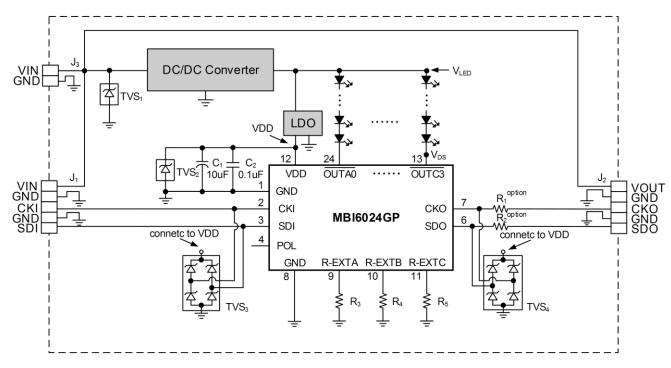

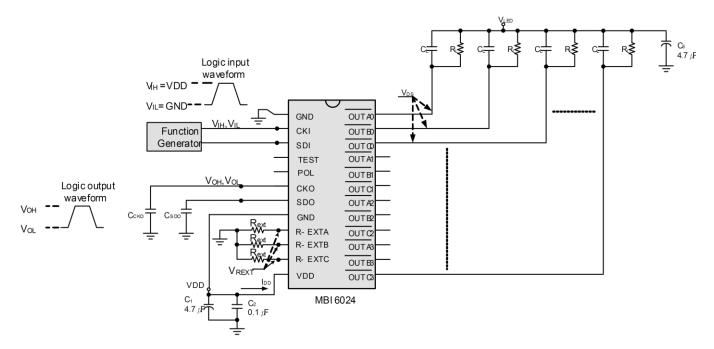

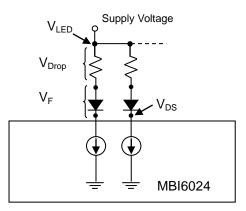

## **Typical Application Circuit**

#### Note:

1.  $TVS_1 \sim TVS_4$  are Transient Voltage Suppressor (TVS).

2.  $C_1 \sim C_2$  are required. The values of the  $C_1 \sim C_2$  are reference only. Tantalum capacitors and Ceramic capacitors are recommended.

3. For hot plug, system grounding, connector design, external ESD protection, or detailed circuit information, please refer to the *"MBI6024 Application Note"* for detailed information.

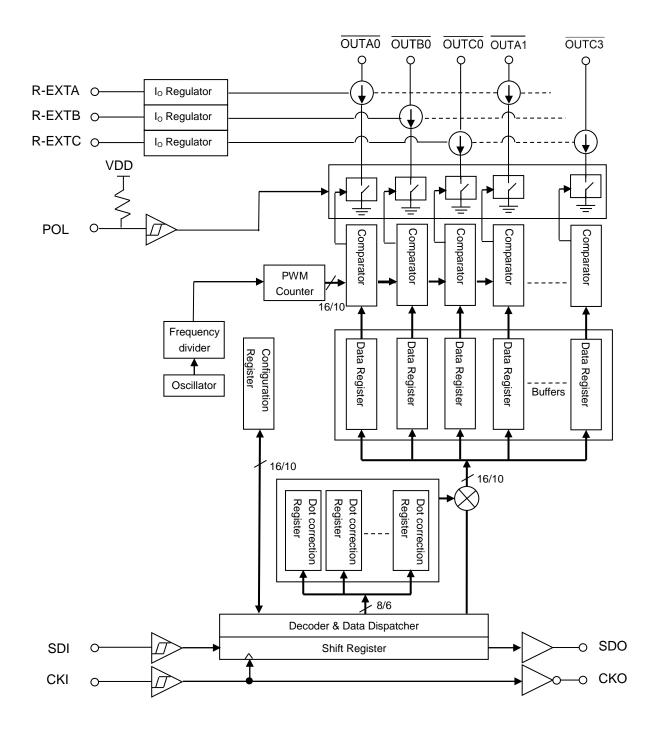

## **Block Diagram**

Sink Driver for LED Strips

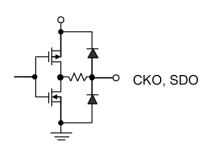

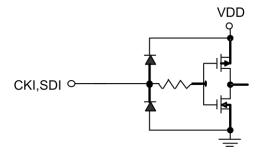

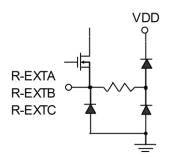

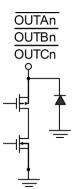

## **Equivalent Circuits of Inputs and Outputs**

CKO, SDO terminal

**CKI, SDI terminal**

R-EXTA, B, C terminal

OUTAn,Bn,Cn terminal

## **Maximum Ratings**

| Characteris                      | tic                                                | Symbol               | Rating                    | Unit |

|----------------------------------|----------------------------------------------------|----------------------|---------------------------|------|

| Supply Voltage                   |                                                    | V <sub>DD</sub>      | 0~7                       | V    |

| Sustaining Voltage at CKI, SDI F | Pins                                               | V <sub>IN</sub>      | -0.4~V <sub>DD</sub> +0.4 | V    |

| Sustaining Voltage at CKO, SDC   | ) Pins                                             | V <sub>OUT</sub>     | -0.4~V <sub>DD</sub> +0.4 | V    |

| Sustaining Voltage at OUTn Pir   | าร                                                 | V <sub>DS</sub>      | -0.5~+17                  | V    |

| Output Current per Output Chan   | nel                                                | Ι <sub>ουτ</sub>     | +45                       | mA   |

| GND Terminal Current             |                                                    | I <sub>GND</sub>     | 570                       | mA   |

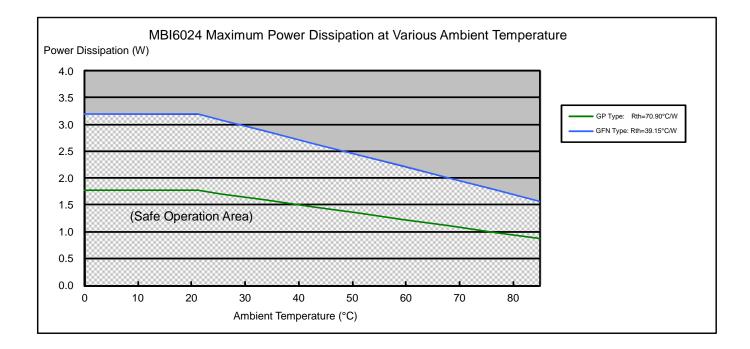

| Heat dissipation                 | GP                                                 | P <sub>D</sub>       | 1.76                      | W    |

| (On 4-Layer PCB, Ta=25°C)*       | GFN                                                | P <sub>D</sub>       | 3.19                      | W    |

| Thermal Resistance               | GP                                                 | R <sub>th(j-a)</sub> | 70.90                     | °C/W |

| (By simulation, on 4-Layer PCB)  | * GFN                                              | R <sub>th(j-a)</sub> | 39.15                     | °C/W |

| Junction Temperature             |                                                    | T <sub>j,max</sub>   | 150**                     | °C   |

| Operating Ambient Temperature    |                                                    | T <sub>opr</sub>     | -40~+85                   | °C   |

| Storage Temperature              |                                                    | T <sub>stg</sub>     | -55~+150                  | °C   |

|                                  | Human Body Mode<br>(MIL-STD-883H<br>Method 3015.8) | НВМ                  | Class 3A<br>(5KV)         | -    |

| ESD Rating                       | Machine Mode<br>(ANSI/ESD<br>S5.2-2009,)           | MM                   | Class M4<br>(400V)        | -    |

\*The PCB size is 76.2mm\*114.3mm in simulation. Please refer to JEDEC JESD51.

\*\* Operation at the maximum rating for extended periods may reduce the device reliability; therefore, the suggested junction temperature of the device is under 125°C.

Note: The performance of thermal dissipation is strongly related to the size of thermal pad, thickness and layer numbers of the PCB. The empirical thermal resistance may be different from simulative value. Users should plan for expected thermal dissipation performance by selecting package and arranging layout of the PCB to maximize the capability.

## Electrical Characteristics (V<sub>pp</sub>=5.0V. Ta=25°C)

|                                                  |                           |                       |                                                        | ov, ra=25                                                      |                           |      |                           |     |

|--------------------------------------------------|---------------------------|-----------------------|--------------------------------------------------------|----------------------------------------------------------------|---------------------------|------|---------------------------|-----|

| Characteris                                      | tics                      |                       |                                                        | Min.                                                           | Тур.                      | Max. | Unit                      |     |

| Supply Voltage                                   |                           | $V_{DD}$              | -                                                      |                                                                | 4.5                       | 5.0  | 5.5                       | V   |

| Sustaining Voltage<br>Ports                      | e at OUT                  | V <sub>DS</sub>       | OUTAn~OUT                                              |                                                                | -                         | -    | 17.0                      | V   |

| Output Current                                   |                           | I <sub>OUT</sub>      | Refer to "Test (<br>Electrical Char                    |                                                                | 5                         | -    | 45                        | mA  |

| Driving Current                                  |                           | I <sub>OH</sub>       | CKO, SDO at \                                          | / <sub>OH</sub> =4.8V                                          | 1.8                       | 2.2  | 2.5                       | mA  |

| Driving Current                                  |                           | I <sub>OL</sub>       | CKO, SDO at \                                          | / <sub>OH</sub> =0.2V                                          | 2.0                       | 2.3  | 2.8                       | mA  |

| Output Leakage C                                 | Surrent                   | Ι <sub>ουτ</sub>      | =Off                                                   | UTAn~OUTCn                                                     | -                         | -    | 1.0                       | μA  |

| Current Skew (Ch                                 | annel)                    | dl <sub>out</sub>     | I <sub>OUT</sub> =20mA<br>V <sub>DS</sub> =1.0V        | R <sub>ext</sub> =7.3KΩ                                        | -                         | ±1.5 | ±3.0                      | %   |

| Current Skew (IC)                                |                           | dl <sub>OUT2</sub>    | I <sub>OUT</sub> =20mA<br>V <sub>DS</sub> =1.0V        | R <sub>ext</sub> =7.3KΩ                                        | -                         | ±3.0 | ±6.0                      | %   |

| Output Current vs.<br>Output Voltage Re          | egulation*                | $%/dV_{DS}$           | %/dV <sub>DS</sub> $V_{DS}$ within 1.0V and 3.0V,      |                                                                | -                         | ±0.1 | ±0.5                      | %/V |

| Output Current vs.<br>Supply Voltage Regulation* |                           | %/dV <sub>DD</sub>    | $V_{\text{DD}}$ within 4.5V and 5.5V                   |                                                                | -                         | ±1.0 | ±2.0                      | %/V |

| Input Voltage of                                 | "H" level                 | V <sub>IH</sub>       | -                                                      |                                                                | 0.73 x<br>V <sub>DD</sub> | -    | $V_{DD}$                  | V   |

| CKI, SDI Pins                                    | "L" level                 | V <sub>IL</sub>       | -                                                      |                                                                | GND                       | -    | 0.28 x<br>V <sub>DD</sub> | V   |

| Output Voltage                                   | "H" level                 | V <sub>OL</sub>       | I <sub>OL</sub> =+3.0mA                                |                                                                | -                         | -    | 0.2                       | V   |

| of CKO, SDO<br>Pins                              | "L" level                 | V <sub>OH</sub>       | I <sub>OH</sub> =-3.0mA                                |                                                                | V <sub>DD</sub> -0.2      | -    | -                         | V   |

| Voltage at R-EXT                                 | A,B,C                     | V <sub>REXT</sub>     | OUTAn~OUT                                              | Cn=On                                                          | 1.1                       | 1.22 | 1.32                      | V   |

| Knee Voltage*                                    |                           | $V_{Knee}$            | R <sub>ext</sub> =3.3KΩ at I                           | <sub>out</sub> =45mA                                           | 0.7                       | 0.75 | 0.8                       | V   |

|                                                  | "Off"                     | I <sub>DD</sub> (off) |                                                        | R <sub>ext</sub> =4.88KΩ, CKI, SDI=Low,<br>CKO, SDO=NC, OUTAn~ |                           | 7.5  | 8.5                       |     |

| Supply Current**                                 | ""                        | L (cc)                | R <sub>ext</sub> =7.3KΩ, CH<br>CKO, SDO=NC<br>OUTCn=On |                                                                | 4.8                       | 5.5  | 6.5                       | mA  |

|                                                  | "On" I <sub>DD</sub> (on) |                       | R <sub>ext</sub> =7.3KΩ, Ck<br>CKO, SDO=NC<br>OUTCn=On |                                                                | -                         | 9    | 10                        |     |

\*One channel turns on.

\*\* The supply current may vary with the loading conditions.

## Electrical Characteristics (V<sub>pp</sub>=3.3V. Ta=25°C)

| Characteris                                                            |                           | Symbol                                                 |                                                                | dition                  | Min.                      | Тур. | Max.                      | Unit |

|------------------------------------------------------------------------|---------------------------|--------------------------------------------------------|----------------------------------------------------------------|-------------------------|---------------------------|------|---------------------------|------|

| Supply Voltage                                                         |                           | V <sub>DD</sub>                                        | -                                                              |                         | 3.0                       | 3.3  | 3.6                       | V    |

| Sustaining Voltage                                                     | e at OUT                  | V <sub>DS</sub>                                        |                                                                | Cn=Off                  | -                         | -    | 17.0                      | V    |

| Output Current                                                         |                           | Ι <sub>ουτ</sub>                                       | Refer to "Test C<br>Electrical Chara                           |                         | 3                         | -    | 30                        | mA   |

| Driving Current                                                        |                           | I <sub>ОН</sub>                                        | CKO, SDO at V                                                  | ′ <sub>он</sub> =3.1V   | 1.6                       | 1.9  | 2.4                       | mA   |

| Driving Current                                                        |                           | I <sub>OL</sub>                                        | CKO, SDO at V                                                  | ′ <sub>он</sub> =0.2V   | 1.6                       | 2.1  | 2.5                       | mA   |

| Output Leakage C                                                       | urrent                    | I <sub>OUT</sub>                                       | V <sub>DS</sub> =17.0V, OU                                     | JTAn~OUTCn              | -                         | -    | 1.0                       | μA   |

| Current Skew (Ch                                                       | annel)                    | dl <sub>out</sub>                                      | I <sub>OUT</sub> =20mA<br>V <sub>DS</sub> =1.0V                | R <sub>ext</sub> =7.3KΩ | -                         | ±1.5 | ±3.0                      | %    |

| Current Skew (IC)                                                      |                           | dl <sub>OUT2</sub>                                     | I <sub>OUT</sub> =20mA<br>V <sub>DS</sub> =1.0V                | R <sub>ext</sub> =7.3KΩ | -                         | ±3.0 | ±6.0                      | %    |

| Output Current vs.<br>Output Voltage Re                                | gulation*                 | $\%/dV_{DS}$                                           | $V_{\text{DS}}$ within 1.0V                                    | and 3.0V                | -                         | ±0.1 | ±0.5                      | %/V  |

| Output Current vs.<br>Supply Voltage %/dV <sub>DD</sub><br>Regulation* |                           | $V_{\text{DD}}$ within 3.0V and 3.6V                   |                                                                | -                       | ±1.0                      | ±2.0 | %/V                       |      |

| Input Voltage of                                                       | "H"<br>level              | V <sub>IH</sub>                                        | -                                                              |                         | 0.73 x<br>V <sub>DD</sub> | -    | $V_{DD}$                  | V    |

| CKI, SDI Pins                                                          | "L"<br>level              | "                                                      |                                                                |                         | GND                       | -    | 0.28 x<br>V <sub>DD</sub> | V    |

| Output Voltage<br>of CKO, SDO                                          | "H"<br>level              | V <sub>OL</sub>                                        | I <sub>OL</sub> =+2.0mA                                        |                         | -                         | -    | 0.2                       | V    |

| Pins                                                                   | "L"<br>level              | V <sub>OH</sub>                                        | I <sub>OH</sub> =-2.0mA                                        |                         | V <sub>DD</sub> -0.2      | -    | -                         | V    |

| Voltage at R-EXT/<br>Pins                                              | A,B,C                     | V <sub>REXT</sub>                                      | OUTAn~OUT                                                      | Cn=On                   | 1.1                       | 1.22 | 1.32                      | V    |

| Knee Voltage*                                                          |                           | V <sub>Knee</sub>                                      | R <sub>ext</sub> =4.88KΩ at                                    | I <sub>OUT</sub> =30mA  | 0.80                      | 0.82 | 0.84                      | V    |

| "Off" I <sub>DD</sub> (                                                |                           | I <sub>DD</sub> (off)                                  | $R_{ext}=4.88K\Omega, C$ $CKO, SDO= NC$ $\overline{OUTCn}=Off$ |                         | -                         | 6.5  | 7.5                       |      |

| Supply Current**                                                       | "ᢕၣ"                      | L_ (00)                                                | R <sub>ext</sub> =7.3KΩ, CK<br>CKO, SDO=NC<br>OUTCn=On         |                         | -                         | 5.5  | 6.5                       | mA   |

|                                                                        | "On" I <sub>DD</sub> (on) | R <sub>ext</sub> =7.3KΩ, CK<br>CKO, SDO=NC<br>OUTCn=On |                                                                | -                       | 6.5                       | 7.5  |                           |      |

\*One channel turns on.

\*\*The supply current may vary with the loading conditions.

## Switching Characteristics (V<sub>DD</sub>=5.0V, Ta=25°C)

| Characteristi                    | CS                                                                                                                                              | Symbol            | Condition                                                              | Min. | Тур. | Max. | Unit  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------|------|------|------|-------|

| Setup Time                       | SDI–CKI↓                                                                                                                                        | t <sub>su</sub>   |                                                                        | 7.5  | -    | -    | ns    |

| Hold Time                        | CKI↓–SDI                                                                                                                                        | t <sub>HD</sub>   |                                                                        | 7.5  | -    | -    | ns    |

|                                  | CKI↑–CKO↓                                                                                                                                       | t <sub>PHL1</sub> |                                                                        | -    | 49   |      | ns    |

|                                  | CKI↓–SDO↑↓                                                                                                                                      | t <sub>PHL2</sub> |                                                                        | -    | 44   |      | ns    |

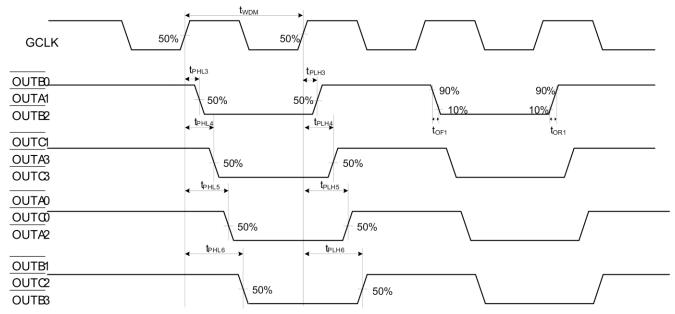

| Propagation<br>Delay Time        | $\operatorname{GCLK}_{\uparrow} = \overline{\operatorname{OUTB0}}, \overline{\operatorname{OUTA1}}, \overline{\operatorname{OUTB2}}$            | t <sub>PHL3</sub> |                                                                        | 22   | 30   | 38   | ns    |

| ("H" to "L")                     | $GCLK_{\uparrow-} \overline{OUTC1}, \overline{OUTA3}, \overline{OUTC3}_{\downarrow}$                                                            | t <sub>PHL4</sub> |                                                                        | 27   | 35   | 43   | ns    |

|                                  | $GCLK_{\uparrow-}\overline{OUTA0},\overline{OUTC0},\overline{OUTA2}\downarrow$                                                                  | t <sub>PHL5</sub> | V <sub>LED</sub> =4V                                                   | 32   | 40   | 48   | ns    |

|                                  | GCLK↑– OUTB1 , OUTC2 , OUTB3 ↓                                                                                                                  | t <sub>PHL6</sub> | V <sub>DS</sub> =1.0V                                                  | 37   | 45   | 53   | ns    |

|                                  | $\operatorname{GCLK}_{\uparrow} = \overline{\operatorname{OUTB0}}, \overline{\operatorname{OUTA1}}, \overline{\operatorname{OUTB2}}_{\uparrow}$ | t <sub>PLH3</sub> | V <sub>IH</sub> =V <sub>DD</sub><br>V <sub>IL</sub> =GND               | 22   | 30   | 38   | ns    |

| Propagation                      | $GCLK_{\uparrow} = \overline{OUTC1}, \overline{OUTA3}, \overline{OUTC3}_{\uparrow}$                                                             | t <sub>PLH4</sub> | I <sub>OUT</sub> =20mA<br>R <sub>L</sub> =150Ω<br>C <sub>L</sub> =10pF | 27   | 35   | 43   | ns    |

| Delay Time<br>("L" to "H")       | $GCLK_{\uparrow} = \overline{OUTA0}, \overline{OUTC0}, \overline{OUTA2}_{\uparrow}$                                                             | t <sub>PLH5</sub> |                                                                        | 32   | 40   | 48   | ns    |

|                                  | GCLK↑– О0ТВ1 , О0ТС2 , О0ТВ3 ↑                                                                                                                  | t <sub>PLH6</sub> | C1=4.7uF<br>C2=0.1uF                                                   | 37   | 45   | 53   | ns    |

| Pulse Width                      | CKI*                                                                                                                                            | t <sub>w(I)</sub> | C3=4.7uF                                                               | 15   | -    | -    | ns    |

| Minimum<br>Pulse Width<br>of PWM | OUTAn~OUTCn                                                                                                                                     | t <sub>WDM</sub>  | С <sub>ско</sub> =8рF<br>С <sub>SDO</sub> =8рF                         | 38   | -    | -    | ns    |

| Rise Time                        | CKO/SDO                                                                                                                                         | t <sub>OR</sub>   |                                                                        | 2.0  | 3.5  | 5.0  | ns    |

|                                  | OUTAn~OUTCn                                                                                                                                     | t <sub>OR1</sub>  |                                                                        | 8.0  | 12.0 | 15.0 | ns    |

| Fall Time                        | CKO/SDO                                                                                                                                         | t <sub>OF</sub>   |                                                                        | 2.0  | 3.5  | 5.0  | ns    |

|                                  | OUTAn~OUTCn                                                                                                                                     | t <sub>OF1</sub>  |                                                                        | 12.0 | 16.0 | 20.0 | ns    |

| <b>F</b>                         | CKI*                                                                                                                                            | F <sub>скі</sub>  |                                                                        | 0.2  | -    | 10   | MHz   |

| Frequency                        | Internal Oscillator                                                                                                                             | F <sub>osc</sub>  |                                                                        | 24   | 26   | 28   | IVITZ |

\*The maximum frequency may be limited by different application conditions. Please refer to the application note for details.

Sink Driver for LED Strips

## Switching Characteristics (V<sub>DD</sub>=3.3V, Ta=25°C)

| Characterist                     | ics                               |                                                      | Symbol            | Condition                                                                          | Min. | Тур. | Max. | Unit |

|----------------------------------|-----------------------------------|------------------------------------------------------|-------------------|------------------------------------------------------------------------------------|------|------|------|------|

| Setup Time                       | SDI–CKI↓                          |                                                      | t <sub>SU</sub>   |                                                                                    | 7.5  | -    | -    | ns   |

| Hold Time                        | CKI↓–SDI                          |                                                      | t <sub>HD</sub>   |                                                                                    | 7.5  | -    | -    | ns   |

|                                  | CKI↑–CKO↓                         |                                                      | t <sub>PHL1</sub> |                                                                                    | -    | 75   | -    | ns   |

|                                  | CKI↓–SDO↑↓                        |                                                      | t <sub>PHL2</sub> |                                                                                    | -    | 67   | -    | ns   |

| Propagatio<br>n Delay            | GCLK↑– OUTB<br>↓                  | $\overline{0}, 000000000000000000000000000000000000$ | t <sub>PHL3</sub> |                                                                                    | 32   | 40   | 48   | ns   |

| Time<br>("H" to "L")             | GCLK∱– ਹਿਸਾਟ<br>↓                 |                                                      | t <sub>PHL4</sub> |                                                                                    | 40   | 48   | 56   | ns   |

|                                  | GCLK↑– OUTA                       |                                                      | t <sub>PHL5</sub> | V <sub>LED</sub> =4V                                                               | 48   | 56   | 64   | ns   |

|                                  | GCLK↑– OUTB                       | 1, ОЛС2, ОЛВ3↓                                       | t <sub>PHL6</sub> | V <sub>DS</sub> =1.0V<br>V <sub>IH</sub> =V <sub>DD</sub>                          | 56   | 64   | 72   | ns   |

|                                  | GCLK↑– OUTB0 , OUTA1 , OUTB2<br>↑ |                                                      | t <sub>PLH3</sub> | V <sub>IL</sub> =GND<br>I <sub>OUT</sub> =20mA                                     | 32   | 40   | 48   | ns   |

| Propagatio<br>n Delay            | GCLK↑– ਹਿਸਾਰ<br>↑                 |                                                      | t <sub>PLH4</sub> | R <sub>L</sub> =150Ω<br>C <sub>L</sub> =10pF<br>C1=4.7uF                           | 40   | 48   | 56   | ns   |

| Time<br>("L" to "H")             | GCLK↑– OUTA                       |                                                      | t <sub>PLH5</sub> | С1=4.7uF<br>C2=0.1uF<br>C3=4.7uF<br>С <sub>ско</sub> =8pF<br>С <sub>SDO</sub> =8pF | 48   | 56   | 64   | ns   |

|                                  | GCLK1- OUTB                       |                                                      | t <sub>PLH6</sub> |                                                                                    | 56   | 64   | 72   | ns   |

| Pulse Width                      | CKI*                              |                                                      | t <sub>w(I)</sub> | OSDO-OPI                                                                           | 20   | -    | -    | ns   |

| Minimum<br>Pulse Width<br>of PWM | OUTAn~OUTCn                       |                                                      | t <sub>WDM</sub>  |                                                                                    | 38   | -    | -    | ns   |

| Rise Time                        | CKO/SDO                           |                                                      | t <sub>OR</sub>   |                                                                                    | 3.0  | 6.0  | 9.0  | ns   |

|                                  | OUTAn~OUT                         | Cn                                                   | t <sub>OR1</sub>  |                                                                                    | 12.0 | 18.0 | 24.0 | ns   |

| Fall Time                        | CKO/SDO                           |                                                      | t <sub>OF</sub>   |                                                                                    | 3.0  | 6.0  | 9.0  | ns   |

|                                  | OUTAn~OUT                         | Cn                                                   | t <sub>OF1</sub>  |                                                                                    | 30.0 | 35.0 | 40.0 | ns   |

| Froquesey                        |                                   | CKI*                                                 | F <sub>CKI</sub>  |                                                                                    | 0.2  | -    | 10   | MHz  |

| Frequency                        |                                   | Internal Oscillator                                  | F <sub>osc</sub>  |                                                                                    | 24   | 26   | 28   |      |

\*The maximum frequency may be limited by different application conditions. Please refer to the application note for details.

Sink Driver for LED Strips

## **Test Circuit for Electrical / Switching Characteristics**

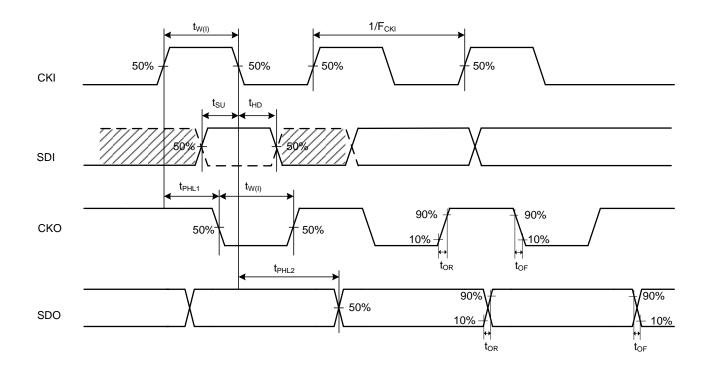

## **Timing Waveform**

Signal Input and Output with Phase-inversed Output Clock

#### **Output Timing**

### **Principle of Operation**

MBI6024 provides SPI-like interface (CKI, SDI), a two-wire transmission interface, to address the data, so that MBI6024 receives the data directly without a latch command. The sequence of operation should follow the steps below:

Step 1. Set the configuration register Step 2. Send the dot correction data Step 3. Send the gray scale data

MBI6024 receives the data packet containing targeted gray scale (GS) data from the controller, and turns on the output channels according to the gray scale data. The gray scale clock of PWM generator, GCLK, is generated by the embedded oscillator.

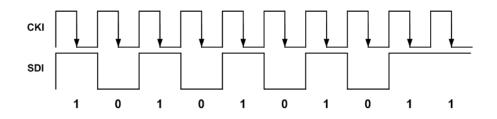

#### Control Interface: SPI-Like Interface (CKI, SDI)

MBI6024 adopts the SPI-like interface (CKI/SDI). By SPI-like interface, MBI6024 samples the data (SDI) at the falling edge of the clock (CKI). The following waveforms is the example of the SPI-like interface.

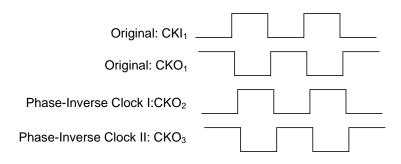

#### Phase-inversed Output Clock

MBI6024 enhances the capability of cascading MBI6024 by phase-inversed output clock function. By phase-inversed output clock, the clock phase will be inversed from CKI to CKO to eliminate the accumulation of the pulse width deviation. This improves the signal integrity of data transmission. The following chart illustrates the phase-inversed output clock results.

#### The Structure of Data Packet

MBI6024's data packet contains three parts:

1. Prefix:

The prefix is a symbol of "Silent-to-Reset", i.e. a time period for MBI6024 to distinguish two data packets. During the prefix, both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

2. Header:

The header defines the cascaded IC numbers and also contains a command to decide the data type.

3. Data:

This is the data for each IC. It may be gray scale data, dot correction data, or configuration data.

Structure of a data packet:

| Prefix Header Data |

|--------------------|

|--------------------|

#### Setting the Data Types by the Command

MBI6024 provides six kinds of commands and input data types shown as the table below:

| Command H[5:0] | Data Type                 |  |

|----------------|---------------------------|--|

| 6'b11 1111     | 16-bit gray scale data    |  |

| 6'b10 1011     | 10-bit gray scale data    |  |

| 6'b11 0011     | 8-bit dot correction data |  |

| 6'b10 0111     | 6-bit dot correction data |  |

| 6'b10 0011     | 16-bit configuration data |  |

| 6'b11 0111     | 10-bit configuration data |  |

Once MBI6024 receives the SDI=1 (1'b1), MBI6024 will start to check if the data is a valid command or not. If the 6-bit data is a valid command, the driver will latch the specific data according to the protocol. If the 6-bit data is not a valid command, MBI6024 will wait for another SDI=1 (1'b1) to check the validity of the next command.

When enable function of polarity reversion, by connecting pin POL to GND, MBI6024 would only accept 10-bit grayscale command listed below

| Command H[5:0] | Data Type              |

|----------------|------------------------|

| 6'b10 1011     | 10-bit gray scale data |

#### Time-Out Reset for Transmission Abort

Time-out reset is to prevent ICs from misreading during the data transmission. If the CKI is tied-low for more than 2 CKI cycles, MBI6024 may identify the wires as disconnection. To prevent from misreading, MBI6024 will ignore the present input data and continuously show the previous image data until the next image data is correctly recognized.

#### The Prefix in the Beginning of a Data Packet

MBI6024 identifies the data as a new data packet after time-out, so the prefix in the beginning of a data packet should be more than 172 CKI cycles.

If both CKI and SDI are tied-low and stop for more than the setting of CKI time-out period, MBI6024 will start to check the valid command of the next data packet. The prefix between two data packets helps MBI6024 identify the

data packet correctly. The following timing diagram illustrates the interval between two data packets in 16-bit gray scale mode.

### **Definition of Configuration Register**

MBI6024 provides two configuration register sections: configuration register 1 (CF1) and configuration register 2 (CF2) as defined in the tables below.

#### Configuration Register 1 (CF1):

|               | MSB |   |   |   |   |   |   |   |   | LSB |

|---------------|-----|---|---|---|---|---|---|---|---|-----|

| Bit           | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| Default Value | 1   | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0   |

Note: Bit [15:10] should be set as "0" to avoid signal misjudgment.

| Bit | Definition              | Value        | Function                                                          |

|-----|-------------------------|--------------|-------------------------------------------------------------------|

|     |                         | 11           | GCLK=frequency of internal oscillator, i.e. 24MHz (typical).      |

| 0.0 | 10 (default)            |              | GCLK=oscillator frequency divided by two, i.e. 12MHz (typical).   |

| 9:8 | GCLK frequency          | 01           | GCLK=oscillator frequency divided by four, i.e. 6MHz (typical).   |

|     |                         | 00           | GCLK= oscillator frequency divided by eight, i.e. 3MHz (typical). |

| 7   | Det correction mode     | 0 (default)  | enable dot correction,                                            |

| 1   | 7 Dot correction mode 1 |              | bypass dot correction                                             |

| 6:5 | Reserved                | 11 (default) | Must fill in '11'                                                 |

|     |                         | 1 (default)  | Reset PWM counter after programming configuration register        |

| 4   | PWM counter reset       |              | Do not reset PWM counter after programming configuration          |

|     |                         | 0            | register                                                          |

| 3   | PWM data                | 1 (default)  | Automatic synchronization                                         |

| 3   | synchronization         | 0            | Manual synchronization                                            |

|     | Phase-inversed          |              | The waveform is inversed from CKI to CKO; please set the two bits |

| 2:1 |                         | 11 (default) | as 2b'11.                                                         |

|     | output clock            |              | Other combinations are reserved for internal tests.               |

|     | Derity check            | 1            | Enable                                                            |

| 0   | Parity check            | 0 (default)  | Disable                                                           |

#### **GCLK Frequency**

MBI6024 provides four kinds of internal GCLK frequency, which is the internal oscillator frequency divided by 1, 2, 4, and 8, for different applications according to the bits of CF1[9:8]. The internal oscillator frequency is 24MHz (typ.); e.g. if the internal oscillator frequency is divided by 8, the GCLK frequency is 3MHz.

Higher GCLK frequency provides higher visual refresh rate, but also higher EMI. If the output current is larger than 40mA, the GCLK frequency is suggested to be lower than 8MHz to keep good linearity at low gray scale level.

#### **Dot Correction Mode**

MBI6024 also provides 8-bit or 6-bit dot correction in 16-bit or 10-bit gray scale mode respectively. Dot correction control helps compensate LED brightness and reduces the loading of calculation in controllers. In addition, with the built-in multiplier, MBI6024 operates dot correction without sacrificing the visual refresh rate.

#### **PWM Counter Reset**

MBI6024 can optionally reset the PWM counter by setting the bit of CF1[4] after programming configuration register. The default setting is to reset the PWM counter to start a new PWM cycle to align the PWM output data for new setting.

#### **PWM Data Synchronization**

MBI6024 is also flexible for either manual-synchronization or auto-synchronization by setting the bit of CF1[3]. For auto-synchronization, the bit of CF1[3] is set to "1" (default). MBI6024 will automatically process the synchronization of previous data and next data for PWM counting. The next image data will be updated to output buffers and start PWM counting when the previous data finishes one internal PWM cycle.

For manual-synchronization, the bit of CF1[3] is set to "0". Once the next input data is correctly recognized, MBI6024 will stop the present PWM cycle and restart a new PWM cycle to show the new data immediately.

The advantage of manual-synchronization is to maintain the synchronization of image frames between ICs, but the PWM cycle may not be finished, so the gray scale accuracy is slightly affected. Since S-PWM scrambles the 16-bit PWM cycle into 64 small periods, the gray scale accuracy remains good. For better gray scale performance, auto-synchronization keeps accurate gray scale especially when using the built-in oscillator, but the drawback is the synchronization of image frames between ICs.

#### Parity Check

Parity check is to check the data in the header for any error, especially to prevent the configuration register and dot correction register from miswriting.

### Configuration Register 2 (CF2):

Default Value

| MSB   |   |     | LSB |

|-------|---|-----|-----|

| Bit   | 2 | 1   | 0   |

| Value |   | 111 |     |

Note: Bit [15:3] should be set as "0" to avoid signal misjudgment.

| Bit | Definition Value |              | Function          |

|-----|------------------|--------------|-------------------|

| 2   | Reserved         | 1 (default)  | Must fill in '1'  |

| 1:0 | Reserved         | 11 (default) | Must fill in '11' |

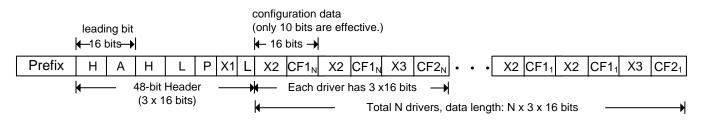

#### **16-bit Configuration Data**

For 16-bit configuration data, each word is 16 bits. Each MBI6024 needs 3 words (3x16=48 bits) for the configuration data. However, each configuration data has only 10 bits, and the MSB 6 bits of each word are invalid. Prior to the configuration data, there is a 48-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:

#### Prefix

Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

#### 48-bits header

|       | to-bits neader |                                 |                                                                                                                 |  |  |

|-------|----------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Bit   | Definition     | Value                           | Function                                                                                                        |  |  |

| 47:42 | H[5:0]         | 100011                          | The command of 16-bit configuration data                                                                        |  |  |

| 41:32 | A[9:0]         | 000000000                       | Address data. Always send 10'b 000000000                                                                        |  |  |

| 31:26 | H[5:0]         | 100011                          | Double check the command. It should be the same as the prior H[5:0], otherwise the data packet will be ignored. |  |  |

| 25:16 | L[9:0]         | N-1<br>N=Number of IC in series | Set the number of IC in series                                                                                  |  |  |

|       |                |                                 | P[3:0] are parity check bits, If it is incorrect, the data packet will                                          |  |  |

|       |                | '[3:0] 0000~1111                | be ignored.                                                                                                     |  |  |

|       | P[3:0]         |                                 | P[0] is the parity check bit of L[9:0]                                                                          |  |  |

|       |                |                                 | P[0]=1 if the count of "1" within L[9:0] is odd;                                                                |  |  |

|       |                |                                 | P[0]=0 if the count of "1" within L[9:0] is even.                                                               |  |  |

| 15:12 |                |                                 | P[1] is the parity check bit of A[9:0]                                                                          |  |  |

|       |                |                                 | P[1]=1 if the count of "1" within A[9:0] is odd;                                                                |  |  |

|       |                |                                 | P[1]=0 if the count of "1" within A[9:0] is even.                                                               |  |  |

|       |                |                                 | P[2] is the parity check bit of H[5:0]                                                                          |  |  |

|       |                |                                 | P[2]=1 if the count of "1" within H[5:0] is odd;                                                                |  |  |

|       |                |                                 | P[2]=0 if the count of "1" within H[5:0] is even.                                                               |  |  |

# PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED Strips

|       |         |                                 | P[3] is the parity check bit of P[2:0]<br>P[3]=1 if the count of "1" within P[2:0] is odd;<br>P[3]=0 if the count of "1" within P[2:0] is even. |

|-------|---------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:10 | X1[1:0] | XX                              | Don't care. The value is suggested to be "0".                                                                                                   |

| 9:0   | L[9:0]  | N-1<br>N=Number of IC in series | Double check the number of IC in series                                                                                                         |

#### 48-bit configuration data

| Bit  | Definition                                                                                            | Value       | Function                                                                              |

|------|-------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|

|      | X2[5:0]~CF1 <sub>N</sub> [9:0]~<br>X2[5:0]~CF1 <sub>N</sub> [9:0]~<br>X3[12:0]~CF2 <sub>N</sub> [2:0] | 48b'0~48b'1 | X2[5:0] are "don't care" bits. The value is suggested to be "0".                      |

|      |                                                                                                       |             | $CF1_N$ [9:0] are 10 bits data of configuration register 1 (CF1). The 2 <sup>nd</sup> |

|      |                                                                                                       |             | CF1[9:0] double checks the data of configuration register bank 1                      |

| 47:0 |                                                                                                       |             | (CF1). It should be the same as the $1^{st}$ CF1 <sub>N</sub> [9:0]; otherwise the    |

|      |                                                                                                       |             | data will not be written into register.                                               |

|      |                                                                                                       |             | X3[12:0] are "don't care" bits. The value is suggested to be "0".                     |

|      |                                                                                                       |             | CF2 <sub>N</sub> [2:0] are 3 bits data of configuration register 2 (CF2)              |

The configuration data of the last IC is sent first, followed by the previous ICs, and the first IC's configuration data is sent in the end of the packet.

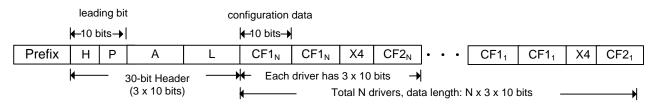

### **10-bit Configuration Data**

For 10-bit configuration data, each word is 10 bits. Each MBI6024 needs 3 words (3x10=30 bits) for the configuration data. Prior to the configuration data, there is a 30-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:

#### Prefix

Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

| Bit   | Definition                                                                           | Value                              | Function                                                                 |

|-------|--------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|

| 29:24 | H[5:0]                                                                               | 110111                             | The command of 10-bit configuration data                                 |

|       |                                                                                      |                                    | P[3:0] are parity check bits, If it is incorrect, the data packet        |

|       |                                                                                      |                                    | will be ignored.                                                         |

|       |                                                                                      |                                    | P[0] is the parity check bit of L[9:0].                                  |

|       |                                                                                      |                                    | P[0]=1 if the count of "1" within L[9:0] is odd;                         |

|       |                                                                                      |                                    | P[0]=0 if the count of "1" within L[9:0] is even.                        |

|       |                                                                                      |                                    | P[1] is the parity check bit of A[9:0]                                   |

| 23:20 | P[3:0]                                                                               | 0000~1111                          | P[1]=1 if the count of "1" within A[9:0] is odd;                         |

| 25.20 | 1 [0.0]                                                                              |                                    | P[1]=0 if the count of "1" within A[9:0] is even.                        |

|       |                                                                                      |                                    | P[2] is the parity check bit of H[5:0]                                   |

|       |                                                                                      |                                    | P[2]=1 if the count of "1" within H[5:0] is odd;                         |

|       |                                                                                      |                                    | P[2]=0 if the count of "1" within H[5:0] is even.                        |

|       |                                                                                      |                                    | P[3] is the parity check bit of P[2:0]                                   |

|       |                                                                                      |                                    | P[3]=1 if the count of "1" within P[2:0] is odd;                         |

|       |                                                                                      |                                    | P[3]=0 if the count of "1" within P[2:0] is even.                        |

| 19:10 | A[9:0]                                                                               | 000000000                          | Address data. Always send 10'b 000000000                                 |

| 9:0   | L[9:0]                                                                               | N-1<br>N=Number of IC<br>in series | Set the number of IC in series                                           |

|       | onfiguration data                                                                    |                                    |                                                                          |

| Bit   | Definition                                                                           | Value                              | Function                                                                 |

|       |                                                                                      | 30b'0~30b'1                        | CF1[9:0] are 10 bits data of configuration register 1 (CF1).             |

| 29:0  | CF1 <sub>N</sub> [9:0]~CF1 <sub>N</sub> [9:<br>0]~X4[6:0]~CF2 <sub>N</sub> [2<br>:0] |                                    | The 2 <sup>nd</sup> CF1[9:0] double checks the data of configuration     |

|       |                                                                                      |                                    | register 1 (CF1). It should be the same as the 1 <sup>st</sup> CF1[9:0]; |

|       |                                                                                      |                                    | otherwise the data will not be written into register.                    |

|       |                                                                                      |                                    | X4[6:0] are "don't care" bits. The value is suggested to be "0"          |

|       |                                                                                      |                                    | CF2[2:0] are 3 bits data of configuration register 2 (CF2)               |

The configuration data of the last IC is sent first, followed by the previous ICs, and the first IC's configuration data is sent in the end of the packet.

### **Gray Scale**

MBI6024 provides two gray scale modes: 16-bit gray scale mode and 10-bit gray scale mode by adopting S-PWM or conventional PWM algorithm respectively. MBI6024 adopts S-PWM technology in 16-bit gray scale mode to scramble the 16-bit PWM to 64 segments, so that the visual refresh rate can be increased. For example, with S-PWM, the default PWM clock (GCLK) frequency is around 12MHz (the frequency of internal oscillator divided by two), and therefore, the visual refresh rate of 16-bit gray scale mode will be increased to: 12MHz/65536x64=11,718Hz

On the other hand, MBI6024 provides 10-bit gray scale mode by conventional PWM. In 16-bit gray scale mode, MBI6024 achieves 65,536 gray scales for each LED, and in 10-bit gray scale mode, MBI6024 achieves 1,024 gray scales. The following illustrations explain the PWM counting by S-PWM and conventional PWM algorithms.

#### PWM counting by S-PWM or conventional PWM algorithm

With S-PWM technology, the total PWM cycles can be broken down into 64 segments.

Example of 16-bit Gray Scale Data:

| Gray scale data | The ratio of output turn-on time in a PWM cycle |

|-----------------|-------------------------------------------------|

| 0               | 0/2 <sup>16</sup>                               |

| 1               | 1/2 <sup>16</sup>                               |

| 2               | 2/2 <sup>16</sup>                               |

|                 |                                                 |

| :               |                                                 |

| 65535           | 65535/2 <sup>16</sup>                           |

Example of 10-bit Gray Scale Data:

| Gray scale data | The ratio of output turn-on time in a PWM cycle |  |

|-----------------|-------------------------------------------------|--|

| 0               | 0/2 <sup>10</sup>                               |  |

| 1               | 1/2 <sup>10</sup>                               |  |

| 2               | 2/2 <sup>10</sup>                               |  |

| •               |                                                 |  |

|                 | :                                               |  |

| 1023            | 1023/2 <sup>10</sup>                            |  |

### 16-bit Gray Scale Data

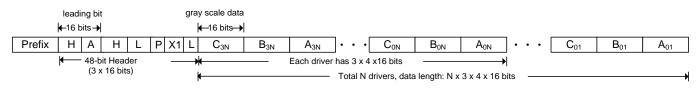

For 16-bit gray scale data, each word is 16 bits. Each MBI6024 needs 12 words (12x16=192 bits) for the gray scale data of each output channel of one MBI6024. Prior to the gray scale data, there is a 48-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:

#### Prefix

Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

#### 48-bit header

| Bit   | Definition | Value                            | Function                                                                                                        |

|-------|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 47:42 | H[5:0]     | 111111                           | The command of 16-bit gray scale data                                                                           |

| 41:32 | A[9:0]     | 000000000                        | Address data. Always send 10'b 000000000                                                                        |

| 31:26 | H[5:0]     | 111111                           | Double check the command. It should be the same as the prior H[5:0], otherwise the data packet will be ignored. |

| 25:16 | L[9:0]     | N -1<br>N=Number of IC in series | Set the number of IC in series                                                                                  |

|       |            |                                  | P[3:0] are parity check bits, If it is incorrect, the data                                                      |

|       |            |                                  | packet will be ignored.                                                                                         |

|       |            |                                  | P[0] is the parity check bit of L[9:0]                                                                          |

|       |            | 0000~1111                        | P[0]=1 if the count of "1" within L[9:0] is odd;                                                                |

|       | P[3:0]     |                                  | P[0]=0 if the count of "1" within L[9:0] is even.                                                               |

|       |            |                                  | P[1] is the parity check bit of A[9:0]                                                                          |

| 15:12 |            |                                  | P[1]=1 if the count of "1" within A[9:0] is odd;                                                                |

| 10.12 |            |                                  | P[1]=0 if the count of "1" within A[9:0] is even.                                                               |

|       |            |                                  | P[2] is the parity check bit of H[5:0]                                                                          |

|       |            |                                  | P[2]=1 if the count of "1" within H[5:0] is odd;                                                                |

|       |            |                                  | P[2]=0 if the count of "1" within H[5:0] is even.                                                               |

|       |            |                                  | P[3] is the parity check bit of P[2:0]                                                                          |

|       |            |                                  | P[3]=1 if the count of "1" within P[2:0] is odd;                                                                |

|       |            |                                  | P[3]=0 if the count of "1" within P[2:0] is even.                                                               |

| 11:10 | X1[1:0]    | XX                               | Don't care. The value is suggested to be "0".                                                                   |

| 9:0   |            | N-1                              | Double check the number of IC in corias                                                                         |

| 9:0   | L[9:0]     | N=Number of IC in series         | Double check the number of IC in series                                                                         |

#### 192-bit gray scale data

| Bit   | Definition                                    | Value         | Function                                                                                                   |

|-------|-----------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------|

| 191:0 | C <sub>3N</sub> [15:0]~A <sub>0N</sub> [15:0] | 192b'0~192b'1 | 16-bit x 12 channels gray scale data of the Nth MBI6024. The data of $\overline{OUTC_{3N}}$ is sent first. |

The gray scale data of the last IC is sent first, followed by the previous ICs, and the first IC's gray scale data is sent in the end of the packet.

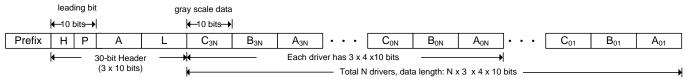

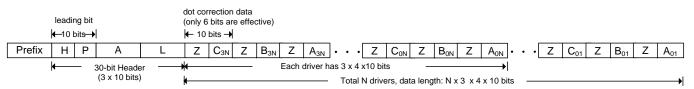

### 10-bit Gray Scale Data

For 10-bit gray scale data, each word is 10 bits. Each MBI6024 needs 12 words (12x10=120 bits) for the gray scale data of each output channel of one MBI6024. Prior to the gray scale data, there is a 30-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:

#### Prefix

Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

| 30-bit | header |

|--------|--------|

|        |        |

| Bit   | Definition | Value                           | Function                                                   |

|-------|------------|---------------------------------|------------------------------------------------------------|

| 29:24 | H[5:0]     | 101011                          | The command of 10-bit gray scale data                      |

|       |            |                                 | P[3:0] are parity check bits, If it is incorrect, the data |

|       |            |                                 | packet will be ignored.                                    |

|       |            |                                 | P[0] is the parity check bit of L[9:0].                    |

|       |            |                                 | P[0]=1 if the count of "1" within L[9:0] is odd;           |

|       |            |                                 | P[0]=0 if the count of "1" within L[9:0] is even.          |

|       | P[3:0]     | 0000~1111                       | P[1] is the parity check bit of A[9:0]                     |

| 23:20 |            |                                 | P[1]=1 if the count of "1" within A[9:0] is odd;           |

| 20.20 |            |                                 | P[1]=0 if the count of "1" within A[9:0] is even.          |

|       |            |                                 | P[2] is the parity check bit of H[5:0]                     |

|       |            |                                 | P[2]=1 if the count of "1" within H[5:0] is odd;           |

|       |            |                                 | P[2]=0 if the count of "1" within H[5:0] is even.          |

|       |            |                                 | P[3] is the parity check bit of P[2:0]                     |

|       |            |                                 | P[3]=1 if the count of "1" within P[2:0] is odd;           |

|       |            |                                 | P[3]=0 if the count of "1" within P[2:0] is even.          |

| 19:10 | A[9:0]     | 000000000                       | Address data. Always send 10'b 000000000                   |

| 9:0   | L[9:0]     | N-1<br>N=Number of IC in series | Set the number of IC in series                             |

#### 120-bit gray scale data

| Bit   | Definition                                  | Value         | Function                                                 |

|-------|---------------------------------------------|---------------|----------------------------------------------------------|

| 119:0 | C <sub>3N</sub> [9:0]~A <sub>0N</sub> [9:0] | 120b'0~120b'1 | 10-bit x 12 channels gray scale data of the Nth MBI6024. |

|       |                                             |               | The data of $\overline{OUTC_{3N}}$ is sent first.        |

The gray scale data of the last IC is sent first, followed by the previous ICs, and the first IC's gray scale data is sent in the end of the packet.

#### **Polarity reversion**

Connecting pin "POL" to GND will enable function of polarity reversion. It will set frequency of internal oscillator to 1.5Mhz and PWM counter to 10-bit mode. Please find more information about it from application note of MBI6024.

#### **Dot Correction**

For valid dot correction control, users have to program dot correction data before sending gray scale data.

#### 16-bit gray scale data with 8-bit dot correction

MBI6024 multiplies the 16-bit gray scale data and 8-bit dot correction data internally and truncates the product to 16 bits, so the PWM cycle time remains 65,536 GCLKs.

The following is the equation for the duty cycle of output in 16-bit gray scale mode. For 8-bit dot correction, the default value of dot correction data is 255.

The duty cycle of output (%) =  $\frac{16\text{-bit gray scale data x}}{65,536} \frac{(8\text{-bit dot correction data + 1})}{256} \times 100\%$

According to the above equation, the following table shows the examples:

| Example:            |                                  |  |  |

|---------------------|----------------------------------|--|--|

| Dot correction data | The ratio of output turn-on time |  |  |

| 0                   | 1/256 x gray scale data          |  |  |

| 1                   | 2/256 x gray scale data          |  |  |

| 2                   | 3/256 x gray scale data          |  |  |

| •                   | •                                |  |  |

| •                   | •                                |  |  |

| · · · ·             | •                                |  |  |

| 255                 | 256/256 x gray scale data        |  |  |

#### 10-bit gray scale with 6-bit dot correction:

The following is the equation for the duty cycle of output in 10-bit gray scale mode. For 6-bit dot correction, the default value of dot correction data is 63.

The duty cycle of output (%) =

$$\frac{10\text{-bit gray scale data x}}{64} \times \frac{(6\text{-bit dot correction data + 1})}{64} \times 100\%$$

According to the above equation, the following table shows the examples: Example:

| Dot correction data | The ratio of output turn-on time |  |

|---------------------|----------------------------------|--|

| 0                   | 1/64 x gray scale data           |  |

| 1                   | 2/64 x gray scale data           |  |

| 2                   | 3/64 x gray scale data           |  |

| •                   | •                                |  |

| :                   | :                                |  |

| 63                  | 64/64 x gray scale data          |  |

#### The algorithm of PWM counting with dot correction data

When adopting 8-bit dot correction in 16-bit gray scale mode, MBI6024 multiplies the 16-bit gray scale data and the 10-bit dot correction data and truncates the product to 16 bits, then uses the corrected 16-bit data to generate PWM output by S-PWM technology. The built-in multiplier facilitates to keep high visual refresh rate.

The chart below illustrates the effect of the built-in multiplier and S-PWM.

Assume:

the 16-bit gray scale data=65,535,

8-bit dot correction data=127 (50%),

then the 16-bit PWM output period is scrambled into 64 segments,

each segment has ~50% duty ratio.

| 16-bit Gray Scale Data<br>with 8-bit Dot<br>Correction Data | 16-bit gray scale=65,535, 8-bit dot correction data=127<br>1024 GCLKs | 62 63 64 |

|-------------------------------------------------------------|-----------------------------------------------------------------------|----------|

|                                                             | Once of 16-bit PWM Counting                                           |          |

When adopting 6-bit dot correction in 10-bit gray scale mode, MBI6024 multiplies the 10-bit gray scale data and the 6-bit dot correction data and truncates the product to 10 bits, then uses the corrected 10-bit data to generate PWM output by S-PWM technology. The built-in multiplier facilitates to keep high visual refresh rate.

The chart below shows the PWM output. Assume: the 10-bit grayscale data=1023, 6-bit dot correction data=31 (50%). the output duty ratio=511/1024(~50%) ° the output duty cycle=1024 GCLKs °

| 10 Gray Scale Data                | 10-bit gray scale data = 1,023, 6-bit dot correction data = 31 |  |  |

|-----------------------------------|----------------------------------------------------------------|--|--|

| with 6-bit Dot<br>Correction Data | 511 GCLKs                                                      |  |  |

|                                   | Once of 10-bit PWM Counting (1,024 GCLKs)                      |  |  |

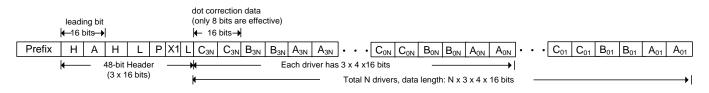

### 8-bit Dot Correction Data

For 8-bit dot correction data, each word is 16 bits. Each MBI6024 needs 12 words (12x16=192 bits) for the dot correction data of each output channel of one MBI6024. However, each dot correction data has only 8 bits, and the first 8 bits of each word are checking bits of dot correction. Prior to the dot correction data, there is a 48-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:

#### Prefix

Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles.

#### 48-bit header

| Bit   | Definition | Value                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------|------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 47:42 | H[5:0]     | 110011                          | The command of 8-bit dot correction data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 41:32 | A[9:0]     | 000000000                       | Address data. Always send 10'b 0000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |